——Rhannwyd o DWIN Froum

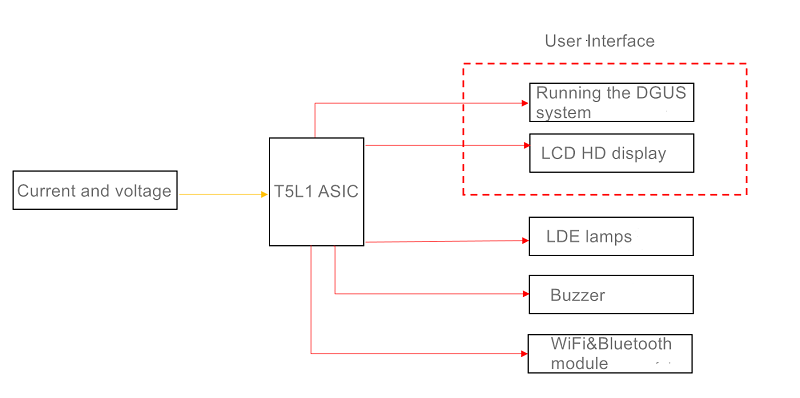

Gan ddefnyddio sglodion DWIN T5L1 fel craidd rheoli'r peiriant cyfan, yn derbyn ac yn prosesu cyffwrdd, caffael ADC, gwybodaeth reoli PWM, ac yn gyrru'r sgrin LCD 3.5-modfedd i arddangos y statws presennol mewn amser real.Cefnogi addasiad cyffyrddiad o bell o ddisgleirdeb ffynhonnell golau LED trwy fodiwl WiFi, a chefnogi larwm llais.

Nodweddion rhaglen:

1. Mabwysiadu sglodion T5L i redeg ar amledd uchel, mae samplu analog AD yn sefydlog, ac mae'r gwall yn fach;

2. Cefnogi MATH C yn uniongyrchol gysylltiedig â PC ar gyfer difa chwilod a llosgi rhaglenni;

3. Cefnogi rhyngwyneb craidd OS cyflym, porthladd cyfochrog 16bit;Porthladd PWM craidd UI, porthladd AD yn arwain allan, dyluniad cymhwysiad cost isel, nid oes angen ychwanegu MCU ychwanegol;

4. Cefnogi WiFi, rheoli o bell Bluetooth;

5. Cefnogi 5 ~ 12V DC foltedd eang a mewnbwn ystod eang

1.1 Diagram cynllun

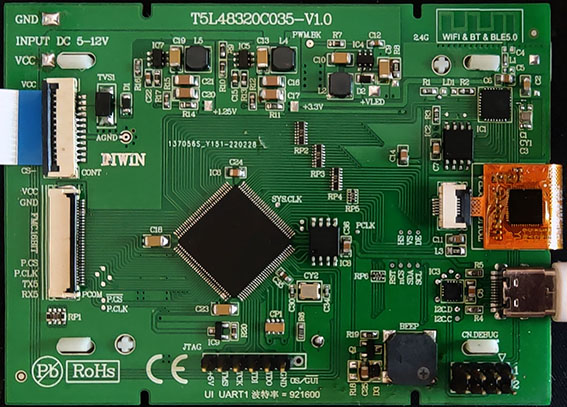

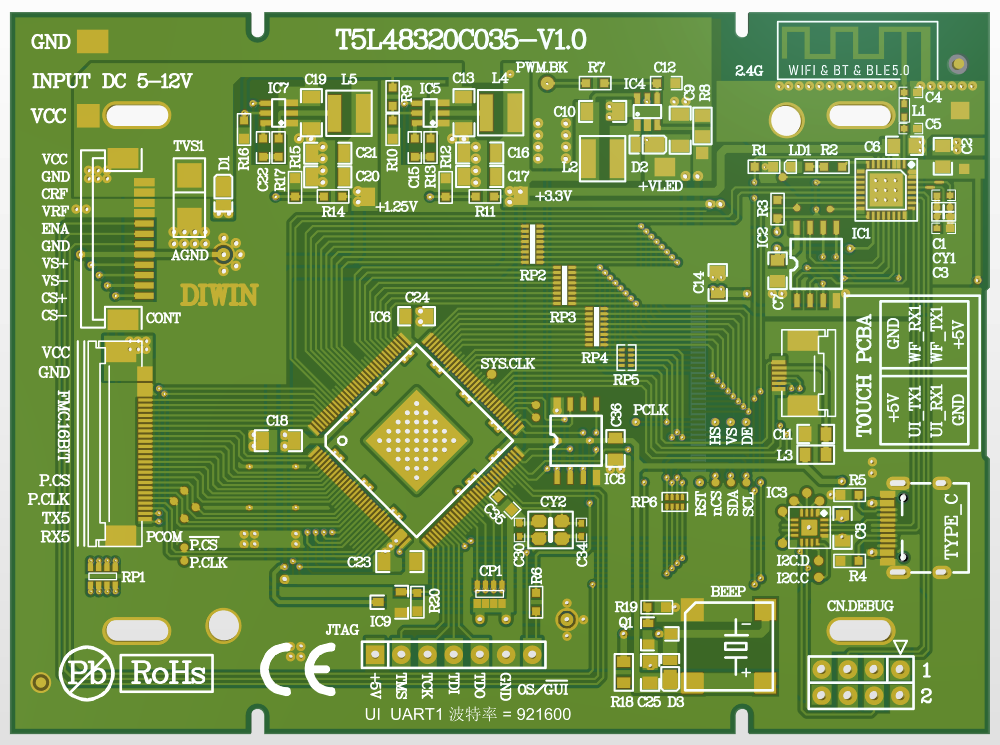

1.2 bwrdd PCB

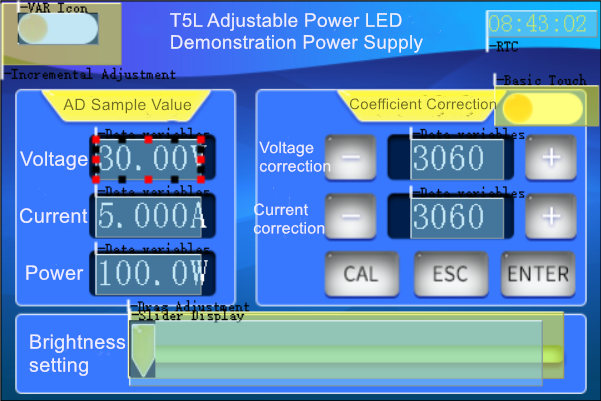

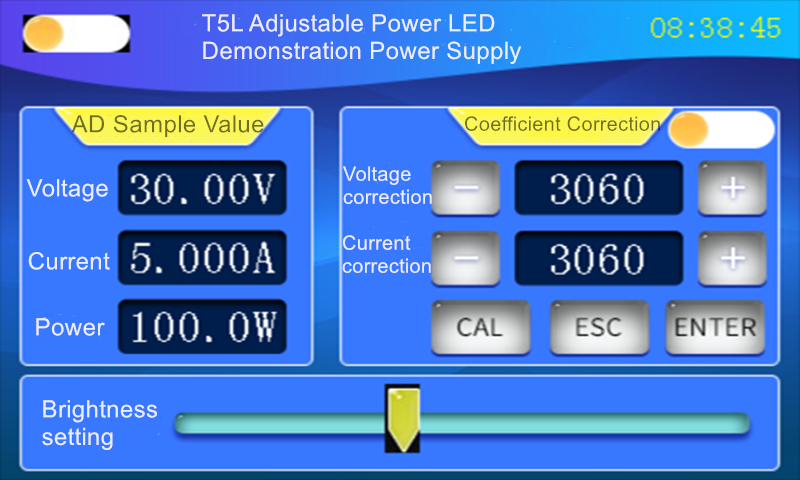

1.3 Rhyngwyneb defnyddiwr

Cyflwyniad cywilydd:

(1) Dyluniad cylched caledwedd

Diagram cylched 1.4 T5L48320C035

1. cyflenwad pŵer rhesymeg MCU 3.3V: C18, C26, C27, C28, C29, C31, C32, C33;

2. cyflenwad pŵer craidd MCU 1.25V: C23, C24;

3. Cyflenwad pŵer analog MCU 3.3V: C35 yw'r cyflenwad pŵer analog ar gyfer MCU.Wrth gysodi, gellir cyfuno'r ddaear graidd 1.25V a'r ddaear rhesymeg gyda'i gilydd, ond rhaid gwahanu'r ddaear analog.Dylid casglu'r ddaear analog a'r ddaear ddigidol wrth begwn negyddol y cynhwysydd LDO allbwn mawr, a dylid casglu'r polyn analog positif hefyd wrth begwn positif y cynhwysydd LDO mawr, fel bod Sŵn samplu AD yn cael ei leihau.

4. Cylched caffael signal analog AD: CP1 yw'r cynhwysydd hidlo mewnbwn analog AD.Er mwyn lleihau'r gwall samplu, mae tir analog a thir digidol yr MCU yn cael eu gwahanu'n annibynnol.Rhaid cysylltu polyn negyddol CP1 â thir analog yr MCU gyda'r rhwystriant lleiaf, ac mae dau gynhwysydd cyfochrog yr osgiliadur grisial wedi'u cysylltu â thir analog yr MCU.

5. Cylched swnyn: C25 yw'r cynhwysydd cyflenwad pŵer ar gyfer y swnyn.Mae'r swnyn yn ddyfais anwythol, a bydd cerrynt brig yn ystod y llawdriniaeth.Er mwyn lleihau'r brig, mae angen lleihau cerrynt gyriant MOS y swnyn i wneud i'r tiwb MOS weithio yn y rhanbarth llinellol, a dylunio'r gylched i wneud iddo weithio yn y modd switsh.Sylwch y dylid cysylltu R18 yn gyfochrog ar ddau ben y swnyn i addasu ansawdd sain y swnyn a gwneud i'r swnyn swnio'n grimp a dymunol.

6. Cylched WiFi: samplu sglodion WiFi ESP32-C, gyda WiFi + Bluetooth + BLE.Ar y gwifrau, mae'r ddaear pŵer RF a'r ddaear signal wedi'u gwahanu.

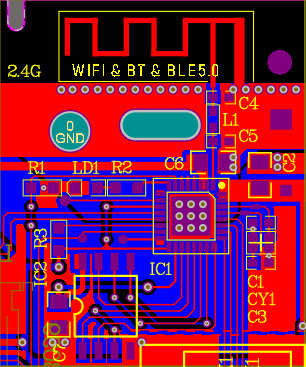

1.5 Dyluniad cylched WiFi

Yn y ffigur uchod, rhan uchaf y cotio copr yw'r ddolen ddaear pŵer.Rhaid i'r ddolen ddaear adlewyrchiad antena WiFi gael ardal fawr i'r ddaear pŵer, a phwynt casglu'r ddaear pŵer yw polyn negyddol C6.Mae angen darparu cerrynt adlewyrchol rhwng y tir pŵer a'r antena WiFi, felly rhaid cael cotio copr o dan yr antena WiFi.Mae hyd y cotio copr yn fwy na hyd estyniad yr antena WiFi, a bydd yr estyniad yn cynyddu sensitifrwydd y WiFi;pwyntio at begwn negatif C2.Gall ardal fawr o gopr gysgodi'r sŵn a achosir gan ymbelydredd antena WiFi.Mae'r 2 sail copr yn cael eu gwahanu ar yr haen isaf a'u casglu i'r pad canol ESP32-C trwy vias.Mae angen rhwystriant is ar y ddaear pŵer RF na dolen ddaear y signal, felly mae 6 vias o'r ddaear pŵer i'r pad sglodion i sicrhau rhwystriant digon isel.Ni all dolen ddaear yr oscillator grisial gael pŵer RF yn llifo drwyddo, fel arall bydd yr osgiliadur grisial yn cynhyrchu jitter amledd, ac ni fydd gwrthbwyso amledd WiFi yn gallu anfon a derbyn data.

7. cylched cyflenwad pŵer backlight LED: samplu sglodion gyrrwr SOT23-6LED.Mae'r cyflenwad pŵer DC / DC i'r LED yn ffurfio dolen yn annibynnol, ac mae'r ddaear DC / DC wedi'i gysylltu â'r ddaear 3.3V LOD.Gan fod craidd porthladd PWM2 wedi'i arbenigo, mae'n allbynnu signal PWM 600K, ac mae RC yn cael ei ychwanegu i ddefnyddio'r allbwn PWM fel rheolydd ON / OFF.

8. Ystod mewnbwn foltedd: mae dau gam-lawr DC/DC wedi'u cynllunio.Sylwch na ellir hepgor y gwrthyddion R13 a R17 yn y gylched DC/DC.Mae'r ddau sglodyn DC / DC yn cefnogi mewnbwn hyd at 18V, sy'n gyfleus ar gyfer cyflenwad pŵer allanol.

9. Porth dadfygio USB MATH C: Gellir plygio MATH C a'i ddad-blygio ymlaen ac yn ôl.Mae mewnosod ymlaen yn cyfathrebu â'r sglodyn WIFI ESP32-C i raglennu'r sglodyn WIFI;mae mewnosodiad gwrthdro yn cyfathrebu â'r XR21V1410IL16 i raglennu'r T5L.Mae MATH C yn cefnogi cyflenwad pŵer 5V.

10. Cyfathrebu porthladd cyfochrog: Mae gan graidd T5L OS lawer o borthladdoedd IO rhad ac am ddim, a gellir dylunio cyfathrebu porthladd cyfochrog 16bit.Wedi'i gyfuno â phrotocol porthladd cyfochrog ST ARM FMC, mae'n cefnogi darllen ac ysgrifennu cydamserol.

11. Dyluniad rhyngwyneb cyflymder uchel LCM RGB: mae allbwn T5L RGB wedi'i gysylltu'n uniongyrchol â LCM RGB, ac ychwanegir ymwrthedd byffer yn y canol i leihau ymyrraeth crychdonnau dŵr LCM.Wrth weirio, lleihau hyd y cysylltiad rhyngwyneb RGB, yn enwedig y signal PCLK, a chynyddu'r rhyngwyneb RGB PCLK, HS, VS, pwyntiau prawf DE;mae porthladd SPI y sgrin wedi'i gysylltu â phorthladdoedd P2.4 ~ P2.7 y T5L, sy'n gyfleus ar gyfer dylunio gyrrwr y sgrin.Arwain pwyntiau prawf RST, nCS, SDA, SCI i hwyluso datblygiad y feddalwedd sylfaenol.

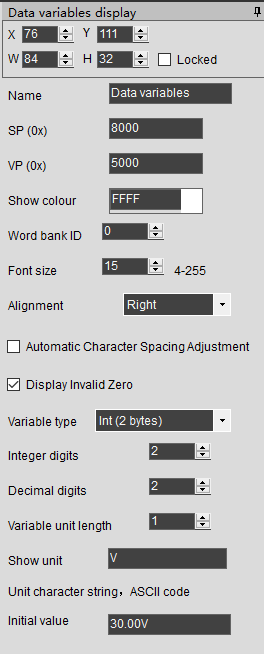

(2) rhyngwyneb DGUS

1.6 Rheolaeth arddangos newidiol data

(3) OS

//—————————— Fformat darllen ac ysgrifennu DGUS

typedef struct

{

u16 addr;// UI cyfeiriad newidiol 16bit

u8 datLen;//8bitdata hyd

u8 *pBuf;//8bit pwyntydd data

} UI_packTypeDef;//DGUS darllen ac ysgrifennu pecynnau

//—————————- rheoli arddangos newidyn data

typedef struct

{

u16 VP;

u16 X;

u16 Y;

u16 Lliw;

u8 Lib_ID;

u8 FontSize;

u8 Algnment;

u8 IntNum;

u8 RhagNum;

u8 Math;

u8 LenUint;

u8 StringUinit[11];

} Nifer_spTypeDef;//data strwythur disgrifiad amrywiol

typedef struct

{

Number_spTypeDef sp;//diffinio pwyntydd disgrifiad SP

UI_packTypeDef spPack;//diffinio SP amrywiol DGUS pecyn darllen ac ysgrifennu

UI_packTypeDef vpPack;//define vp variable DGUS pecyn darllen ac ysgrifennu

} Number_HandleTypeDef;//data strwythur newidiol

Gyda diffiniad handlen y newidyn data blaenorol.Nesaf, diffiniwch newidyn ar gyfer yr arddangosfa samplu foltedd:

Number_HandleTypeDef Hsample;

u16 foltedd_sample;

Yn gyntaf, gweithredwch y swyddogaeth gychwynnol

NumberSP_Init(&Hsample,voltage_sample, 0×8000);//0×8000 dyma'r pwyntydd disgrifiad

//——Newidyn data yn dangos cychwyniad strwythur pwyntydd SP——

gwagle NumberSP_Init(Number_HandleTypeDef *rhif, u8 *gwerth, u16 numberAddr)

{

number->spPack.addr = numberAddr;

number-> spPack.datLen = sizeof(rhif->sp);

number->spPack.pBuf = (u8*)&rhif->sp;

Read_Dgus(&rhif-> spPack);

number->vpPack.addr = rhif->sp.VP;

switsh (rhif-> sp.Type) // Mae hyd data'r newidyn vp yn cael ei ddewis yn awtomatig yn ôl y math o newidyn data a ddyluniwyd yn y rhyngwyneb DGUS.

{

achos 0:

achos 5:

number->vpPack.datLen = 2;

torri;

achos 1:

achos 2:

achos 3:

achos 6:

number->vpPack.datLen = 4;

achos 4:

number->vpPack.datLen = 8;

torri;

}

number->vpPack.pBuf = gwerth;

}

Ar ôl ymgychwyn, Hsample.sp yw'r pwyntydd disgrifiad o'r newidyn data samplu foltedd;Hsample.spPack yw'r pwyntydd cyfathrebu rhwng craidd yr OS a'r newidyn data samplu foltedd UI trwy swyddogaeth rhyngwyneb DGUS;Hsample.vpPack yw'r priodoledd o newid y newidyn data samplu foltedd, megis Lliwiau ffont, ac ati hefyd yn cael eu trosglwyddo i'r craidd UI trwy swyddogaeth rhyngwyneb DGUS.Hsample.vpPack.addr yw cyfeiriad newidyn data samplu foltedd, sydd wedi'i gael yn awtomatig o'r swyddogaeth cychwyn.Pan fyddwch chi'n newid y cyfeiriad newidiol neu'r math o ddata amrywiol yn y rhyngwyneb DGUS, nid oes angen diweddaru'r cyfeiriad newidiol yn y craidd OS yn gydamserol.Ar ôl i'r craidd OS gyfrifo'r newidyn foltedd_sample, dim ond y swyddogaeth Write_Dgus(&Hsample.vpPack) sydd ei angen i'w ddiweddaru.Nid oes angen pacio'r foltedd_sample ar gyfer trosglwyddo DGUS.

Amser postio: Mehefin-15-2022