Manyleb

| T5L ASIC | Cynlluniwyd gan DWIN.Cynhyrchu màs yn 2019, 1MBytes Nor Flash ar y sglodyn, 512KBytes a ddefnyddir i storio'r gronfa ddata defnyddwyr.Ailysgrifennu cylch: dros 100,000 o weithiau | |

| Lliw | 262K (262144) lliwiau | |

| Math LCD | IPS | |

| Gweld Ongl | Ongl gwylio eang, 85 ° / 85 ° / 85 ° / 85 ° (L / R / U / D) | |

| Ardal Arddangos (AA) | 70.08mm (W) × 52.56mm (H) | |

| Datrysiad | 320 × 240 picsel | |

| Golau cefn | LED | |

| Disgleirdeb | EKT035A: addasiad lefel 270nit 100. (Nid yw'n argymell gosod disgleirdeb i 1% ~ 30% o'r uchafswm, a all arwain fflachiad) | |

| LED Oes | ≥20000H (Gweithio'n barhaus gyda'r disgleirdeb mwyaf, mae amser y disgleirdeb yn pydru i 50%) | |

| Foltedd Pŵer | 6 ~ 36V | |

| Gweithrediad Cyfredol | VCC = +12V, Backlight ymlaen,90mA | |

| VCC = +12V, Backlight i ffwrdd, 30mA | ||

| Tymheredd Gweithio | -20 ~ 70 ℃ (Arferol 25 ℃) | |

| Tymheredd Storio | -30 ~ 85 ℃ (Arferol 25 ℃) | |

| Lleithder Gweithio | 10% ~ 90% RH (Arferol 25 ℃) | |

| Soced | 50Pin-0.5mm FCC | |

| USB | OES | |

| Slot SD | OES (Fformat SDHC/FAT32) | |

| Fflach | Gofod Ffont: 4-12Mbytes | |

| Storio Llun: 12-4Mbytes | ||

| Ram | 128Kbeit | |

| Na Flash | 512Kbeit | |

| Fersiwn UI | TA / DGUSⅡ (DGUSⅡ wedi'i osod ymlaen llaw) | |

| Ymylol | Panel cyffwrdd capacitive, Buzzer | |

| Dimensiwn | 131.39mm (W) × 83.64mm(H) × 17.75mm(T) | |

| Pwysau Net | 105g | |

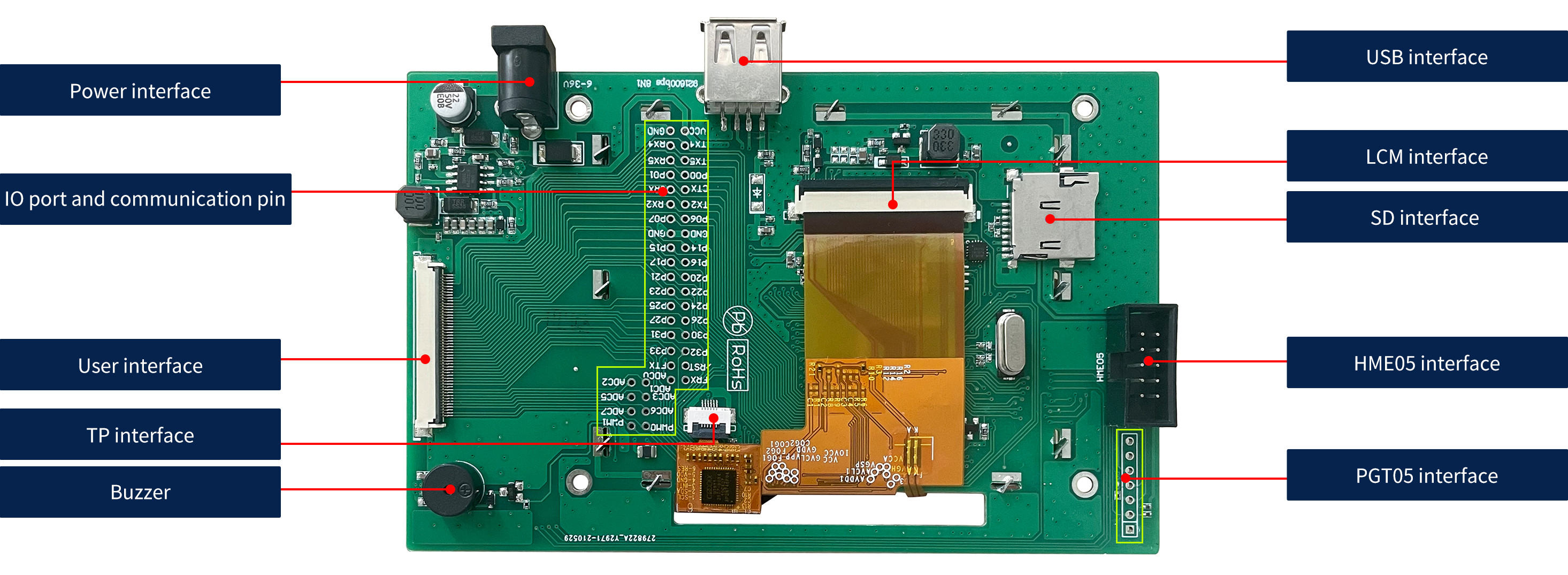

| 1# | Rhyngwyneb cyflenwad pŵer foltedd eang 6-36V | |

| 2# | Rhyngwyneb USB, gellir dewis UART1 | |

| 3# | Modiwl ehangu FLASH, gellir ehangu 3 modiwl FLASH | |

| 4# | Pad twll trwodd 2.54mm, i dynnu'r rhyngwyneb adnoddau defnyddiwr, 20 porthladd IO, 3 porthladd cyfresol UART, ac 1 porthladd CAN 7 porthladd AD a 2 borthladd PWM | |

| 5# | Rhyngwyneb JTAG, cysylltu ag efelychydd HME05, neu gysylltu â llosgydd PGT05 i losgi'r firmware craidd sylfaenol. | |

| PIN | Diffiniad | Disgrifiad |

| 1# | GND | Tir cyffredin |

| 2# | RX4 | UART4 Derbyn data |

| 3# | RX5 | UART5 Derbyn data |

| 4# | P01 | wyf / O enau |

| 5# | CRX | Derbyniad data rhyngwyneb CAN |

| 6# | RX2 | Derbyn data UART2 |

| 7# | T07 | Rwyf / O |

| 8# | t15 | Rwyf / O |

| 9# | t17 | Rwyf / O |

| 10# | t21 | Rwyf / O |

| 11# | t23 | Rwyf / O |

| 12# | t25 | Rwyf / O |

| 13# | t27 | Rwyf / O |

| 14# | t31 | Rwyf / O |

| 15# | t33 | Rwyf / O |

| 16# | FTX | Derbyniad data transceiver FSK |

| 17# | ADC0 | Mewnbwn AD |

| 18# | ADC2 | Mewnbwn AD |

| 19# | ADC5 | Mewnbwn AD |

| 20# | ADC7 | Mewnbwn AD |

| 21# | PWM1 | Allbwn PWM 16bit |

| 22# | VCC | mewnbwn pŵer |

| 23# | TX4 | Trosglwyddo data UART4 |

| 24# | TX5 | Trosglwyddo data UART5 |

| 25# | P0.0 | Rwyf / O |

| 26# | CTX | CAN trosglwyddo data rhyngwyneb |

| 27# | TX2 | Trosglwyddo data UART2 |

| 28# | P06 | Rwyf / O |

| 29# | t14 | Rwyf / O |

| 30# | t16 | Rwyf / O |

| 31# | t20 | Rwyf / O |

| 32# | t22 | Rwyf / O |

| 33# | t24 | Rwyf / O |

| 34# | t26 | Rwyf / O |

| 35# | P30 | Rwyf / O |

| 36# | t32 | Rwyf / O |

| 37# | RST | Mewnbwn ailosod system |

| 38# | FRX | Trosglwyddo data transceiver FSK |

| 39# | ADC1 | Mewnbwn AD |

| 40# | ADC3 | Mewnbwn AD |

| 41# | ADC6 | Mewnbwn AD |

| 42# | PWM0 | Allbwn PWM 16bit |