Manyleb

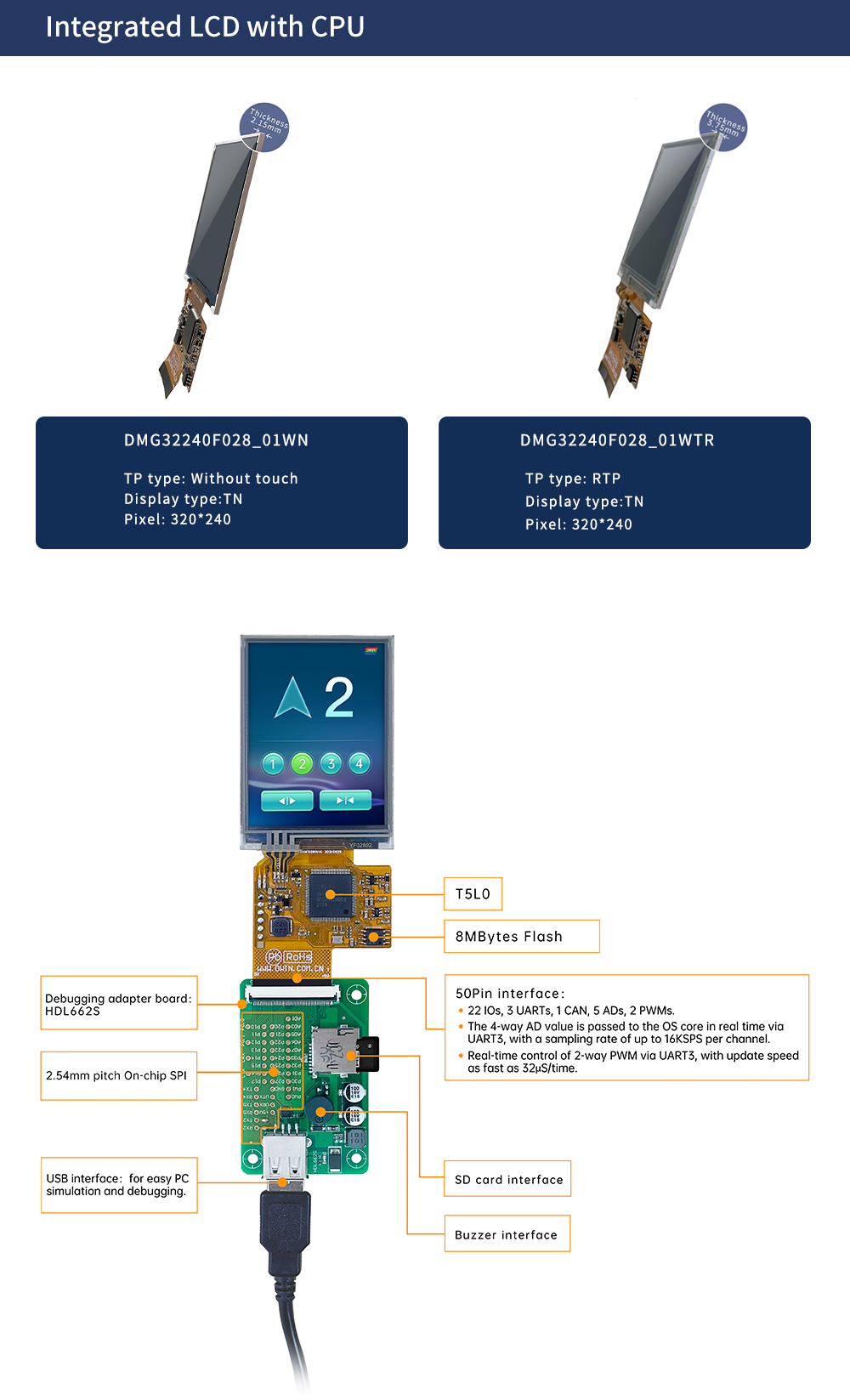

| T5L0 ASIC | Mae T5L0 ASIC yn GUI pŵer isel, cost-effeithiol, a chymhwysiad ASIC craidd deuol un sglodyn hynod integredig a ddyluniwyd gan DWIN Technology ar gyfer LCD maint bach a màs a gynhyrchir yn 2020. | ||

| Lliw | lliwiau 262K | ||

| Math LCD | TN, TFT LCD | ||

| Gweld Ongl | Ongl wylio arferol, gwerth nodweddiadol o 70 ° / 70 ° / 50 ° / 70 ° (L / R / U / D) | ||

| Ardal Arddangos (AA) | 43.2mm(W) × 57.6mm(H) | ||

| Datrysiad | 240*320 | ||

| Golau cefn | LED | ||

| Disgleirdeb | DMG32240F028_01WN: 350nit DMG32240F028_01WTR: 300nit | ||

| Math | RTP (Panel Cyffwrdd Gwrthiannol) | ||

| Strwythur | Ffilm ITO + gwydr ITO | ||

| Modd Cyffwrdd | Cefnogi pwynt cyffwrdd a llusgo | ||

| Caledwch Arwyneb | 3H | ||

| Trosglwyddiad Ysgafn | Dros 80% | ||

| Bywyd | Dotio > 1,000,000 o weithiau;Strôc > 100,000 o weithiau;150g grym, yn ôl ac ymlaen yn cyfrif fel ddwywaith | ||

| Foltedd Pŵer | 3.6 ~ 5.5V, gwerth nodweddiadol o 5V | ||

| Gweithrediad Cyfredol | 110mA VCC=5V, golau ôl mwyaf | ||

| WTC:- WN:75mA VCC=5V, golau cefn i ffwrdd | |||

| Tymheredd Gweithio | -10 ℃ ~ 60 ℃ | ||

| Tymheredd Storio | -20 ℃ ~ 70 ℃ | ||

| Lleithder Gweithio | 10% ~ 90% RH, gwerth nodweddiadol o 60% RH | ||

| Rhyngwyneb defnyddiwr | 50Pin_0.5mm FPC | ||

| Baudrate | 3150 ~ 3225600bps | ||

| Foltedd Allbwn | Allbwn 1; 3.0 ~ 3.3 V | ||

| Allbwn 0; 0 ~ 0.3 V | |||

| Foltedd Mewnbwn (RXD) | Mewnbwn 1;3.3V | ||

| Mewnbwn 0;0~0.5V | |||

| Rhyngwyneb | UART2: TTL; UART4: TTL; (Dim ond ar gael ar ôl cyfluniad OS UART5: TTL; (Dim ond ar gael ar ôl ffurfweddiad OS) | ||

| Fformat Data | UART2: N81; UART4: N81/E81/O81/N82; 4 modd (cyfluniad OS) UART5: N81/E81/O81/N82; 4 modd (cyfluniad OS) | ||

| Pin | Diffiniad | I/O | Disgrifiad Swyddogaethol |

| 1 | 5V | I | Cyflenwad pŵer, DC3.6-5.5V |

| 2 | 5V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | OC7 | I | 5 ADC mewnbwn.Datrysiad 12-did rhag ofn y bydd cyflenwad pŵer 3.3V.Foltedd mewnbwn 0-3.3V.Ac eithrio AD6, anfonir y data gweddill i graidd OS trwy UART3 mewn amser real gyda chyfradd samplu 16KHz.Gellir defnyddio AD1 ac AD5 yn gyfochrog, a gellir defnyddio AD3 ac AD7 yn gyfochrog, sy'n hafal i ddau samplu 32KHz AD.Gellir defnyddio AD1, AD3, AD5, AD7 yn gyfochrog, sy'n cyfateb i AD samplu 64KHz;mae'r data'n cael ei grynhoi 1024 o weithiau ac yna'n cael ei rannu â 64 i gael gwerth AD 64Hz 16bit trwy orsamplu. |

| 7 | OC6 | I | |

| 8 | OC5 | I | |

| 9 | OC3 | I | |

| 10 | OC2 | I | |

| 11 | 3.3 | O | Allbwn 3.3V, llwyth uchaf o 150mA. |

| 12 | SPK | O | MOSFET allanol i yrru swnyn neu siaradwr.Dylid tynnu'r gwrthydd 10K allanol i lawr i'r llawr i sicrhau bod pŵer ymlaen yn lefel isel. |

| 13 | SD_CD | I/O | Rhyngwyneb SD/SDHC, Mae'r SD_CK yn cysylltu cynhwysydd 22pF i GND ger y rhyngwyneb cerdyn SD. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | I/O | |

| 16 | SD_D2 | I/O | |

| 17 | SD_D1 | I/O | |

| 18 | SD_D0 | I/O | |

| 19 | PWM0 | O | 2 allbwn PWM 16-did.Dylid tynnu'r gwrthydd 10K allanol i lawr i'r llawr i sicrhau bod pŵer ymlaen yn lefel isel. Gellir rheoli craidd yr AO mewn amser real trwy UART3 |

| 20 | PWM1 | O | |

| 21 | t3.3 | I/O | Os ydych chi'n defnyddio RX8130 neu SD2058 I2C RTC i gysylltu â'r ddau IO, dylid cysylltu SCL â P3.2, a SDA wedi'i gysylltu â P3.3 ochr yn ochr â gwrthydd 10K tynnu hyd at 3.3V. |

| 22 | t3.2 | I/O | |

| 23 | P3.1/EX1 | I/O | Gellir ei ddefnyddio fel mewnbwn ymyrraeth allanol 1 ar yr un pryd, ac mae'n cefnogi lefel foltedd isel neu foddau ymyrraeth ymylol. |

| 24 | P3.0/EX0 | I/O | Gellir ei ddefnyddio fel ymyrraeth allanol 0 mewnbwn ar yr un pryd, ac mae'n cefnogi lefel foltedd isel neu foddau ymyrraeth ymylol. |

| 25 | t2.7 | I/O | rhyngwyneb IO |

| 26 | t2.6 | I/O | rhyngwyneb IO |

| 27 | t2.5 | I/O | rhyngwyneb IO |

| 28 | t2.4 | I/O | rhyngwyneb IO |

| 29 | t2.3 | I/O | rhyngwyneb IO |

| 30 | P2.2 | I/O | rhyngwyneb IO |

| 31 | t2.1 | I/O | rhyngwyneb IO |

| 32 | t2.0 | I/O | rhyngwyneb IO |

| 33 | P1.7 | I/O | rhyngwyneb IO |

| 34 | t1.6 | I/O | rhyngwyneb IO |

| 35 | P1.5 | I/O | rhyngwyneb IO |

| 36 | P1.4 | I/O | rhyngwyneb IO |

| 37 | P1.3 | I/O | rhyngwyneb IO |

| 38 | P1.2 | I/O | rhyngwyneb IO |

| 39 | P1.1 | I/O | rhyngwyneb IO |

| 40 | t1.0 | I/O | rhyngwyneb IO |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | I/O | rhyngwyneb IO |

| 46 | P0.1 | I/O | rhyngwyneb IO |

| 47 | CAN_TX | O | CAN rhyngwyneb |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2 (porth cyfresol UART0 o graidd OS) |

| 50 | UART2_RXD | I |

Model: TC040C12 U(W) 00

Model: DMG48320F035_01W (Cyfres COF)